# L4 eXperimental Kernel Reference Manual

Version X.2

System Architecture Group Dept. of Computer Science Universität Karlsruhe (L4Ka Team) 14spec@14ka.org

Document Revision 6 November 17, 2006

# **Contents**

| Al |                                          | vi  |

|----|------------------------------------------|-----|

|    | Introductory Remarks                     | vi  |

|    | Understanding This Document              | vii |

|    | Notation                                 | i>  |

|    | Using the API                            |     |

|    | Revision History                         | X   |

| 1  | Basic Kernel Interface                   | 1   |

| •  | 1.1 Kernel Interface Page                | -   |

|    | 1.2 KernelInterface                      |     |

|    | 1.3 Virtual Registers                    |     |

|    |                                          |     |

| 2  | Threads                                  | 13  |

|    | 2.1 ThreadId                             |     |

|    | 2.2 Thread Control Registers (TCRs)      |     |

|    | 2.3 EXCHANGEREGISTERS                    |     |

|    | 2.4 ThreadControl                        | 22  |

| 3  | Scheduling                               | 25  |

|    | 3.1 Clock                                | 26  |

|    | 3.2 SystemClock                          | 27  |

|    | 3.3 Time                                 | 28  |

|    | 3.4 ThreadSwitch                         | 30  |

|    | 3.5 SCHEDULE                             |     |

|    | 3.6 Preempt Flags                        | 35  |

| 4  | Address Spaces and Mapping               | 37  |

| •  | 4.1 Fpage                                |     |

|    | 4.2 UNMAP                                |     |

|    | 4.3 SpaceControl                         |     |

|    |                                          |     |

| 5  | IPC                                      | 47  |

|    | 5.1 Messages And Message Registers (MRs) |     |

|    | 5.2 MapItem                              |     |

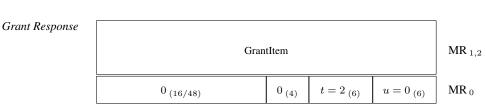

|    | 5.3 GrantItem                            |     |

|    | 5.4 StringItem                           |     |

|    | 5.6 IPC                                  |     |

|    | 5.0 110                                  | 0.  |

| 6  | Miscellaneous                            | 69  |

|    | 6.1 ExceptionHandler                     | 70  |

|    | 6.2 Cop Flags                            |     |

|    | 6.3 ProcessorControl                     |     |

|    | 6.4 MEMORYCONTROL                        | 74  |

| 7  | Protocols                                | 77  |

| •  | 7.1 Thread Start Protocol                | 78  |

|    | 7.2 Interrupt Protocol                   | 79  |

|    | 7.3 Pagefault Protocol                   | 80  |

|    | 7.4 Preemption Protocol                  | 81  |

|    | 7.5 Exception Protocol                   | 82  |

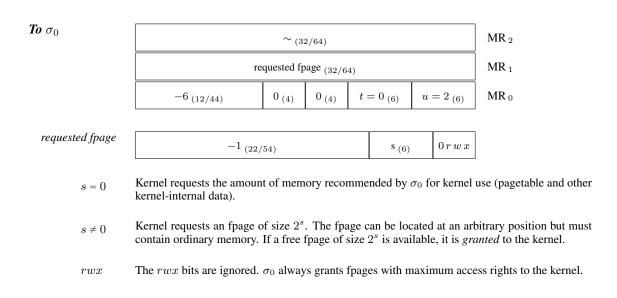

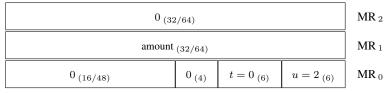

|    | 7.6 Sigma0 RPC protocol                  | 83  |

|    | 7.7 Generic Rooting                      | 26  |

iv CONTENTS

| Δ | TA-3        | 32 Interface             | 89         |

|---|-------------|--------------------------|------------|

| 7 |             | Virtual Registers        |            |

|   |             |                          |            |

|   |             | Systemcalls              |            |

|   |             | Kernel Features          |            |

|   |             | IO Ports                 |            |

|   |             | Space Control            |            |

|   |             | Cacheability Hints       |            |

|   | A.7         | Memory Attributes        | 00         |

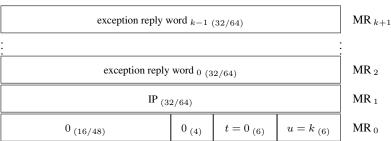

|   | A.8         | Exception Message Format | 01         |

|   | A.9         | Processor Mirroring      | 02         |

|   | A.10        | ) Booting                | 03         |

|   |             |                          |            |

| В |             | -                        | 05         |

|   | B.1         | Virtual Registers        | 06         |

|   | B.2         | PAL and SAL Access       | 08         |

|   |             | Systemcalls              |            |

|   |             | PCI Configuration Space  |            |

|   |             | Cacheability Hints       |            |

|   |             | Memory Attributes        |            |

|   |             |                          |            |

|   |             | Memory Descriptors       |            |

|   | В.8         | Exception Message Format | 18         |

| ~ | ъ           | POT 4 A                  | 10         |

| C |             |                          | 19         |

|   |             | Virtual Registers        |            |

|   |             | Systemcalls              |            |

|   |             | Memory Attributes        |            |

|   |             | Exception Message Format |            |

|   | C.5         | Processor Mirroring      | 29         |

|   | C.6         | Booting                  | 30         |

|   |             |                          |            |

| D |             |                          | 31         |

|   | D.1         | Virtual Registers        | 32         |

|   |             | Systemcalls              |            |

|   |             | Memory Attributes        |            |

|   |             | Exception Message Format |            |

|   |             | Booting                  |            |

|   | <b>D</b> .5 | 20011115                 |            |

| E | Alp         | ha Interface 1           | 43         |

| _ | E 1         | Virtual Registers        |            |

|   |             | Systemcalls              |            |

|   |             | Booting                  |            |

|   | E.J         | Booting                  | 50         |

| F | мп          | PS-64 Interface          | 51         |

| r |             | Virtual Registers        |            |

|   |             | Systemcalls              |            |

|   |             |                          |            |

|   |             | Memory Attributes        |            |

|   |             | Exception Message Format |            |

|   | F.5         | Booting                  | 62         |

| ~ |             |                          |            |

| G |             |                          | 63         |

|   | G.1         | Virtual Registers        |            |

|   | G.2         |                          |            |

|   | G.3         | IO Ports                 | 72         |

|   | G.4         | Cacheability Hints       | 73         |

|   | G.5         | Memory Attributes        | 74         |

|   | G.6         | Exception Message Format | 75         |

|   |             | Processor Mirroring      |            |

|   |             | Booting                  |            |

|   |             |                          | ĺ          |

| Н | SPA         | RC v9 Interface          | <b>7</b> 9 |

|   | H.1         | Virtual Registers        | 80         |

|   |             | Systemcalls              |            |

|   |             | •                        |            |

CONTENTS

| I  | ARM Interface                       | 187   |

|----|-------------------------------------|-------|

|    | I.1 Virtual Registers               | . 188 |

|    | I.2 Systemcalls                     | . 190 |

|    | I.3 Memory Attributes               | . 193 |

|    | I.4 Space Control                   | . 194 |

|    | I.5 Exception Message Format        |       |

|    | I.6 Booting                         |       |

| J  | Generic BootInfo                    | 199   |

| -  | J.1 Generic BootInfo                | . 200 |

|    | J.2 BootInfo Records                |       |

| K  | Development Remarks                 | 205   |

|    | K.1 Exception Handling              | . 205 |

| Ta | able of Procs, Types, and Constants | 207   |

|    | •                                   | 215   |

| In | ndex                                | 215   |

vi *CONTENTS*

# **About This Manual**

# **Introductory Remarks**

# **Purpose of This Document**

This L4 Reference Manual serves as defining document for all L4 APIs and ABIs. Primarily, it addresses L4 microkernel implementors as API/ABI suppliers and code-generator or library implementors as API/ABI users. The reference manual assumes intimate knowledge of basic L4 concepts and hardware architecture. Its key point is precise definition, not explanation and illustration. The

#### L4 System Programmer's Manual

is intended to support programmers using L4. It explains and illustrates fundamental concepts and describes in more detail how (and why) to use which function, etc.

## **Maintainers**

The document is maintained by the following members of the L4Ka Team:

- Uwe Dannowski (ud3@ira.uka.de)

- Joshua LeVasseur (jtl@ira.uka.de)

- Espen Skoglund (esk@ira.uka.de)

- Volkmar Uhlig (volkmar@ira.uka.de)

# Credits

This manual is based on a final draft by **Jochen Liedtke**. It reflects his outstanding work on the L4 microkernel and systems research in general. Only his vision of system design made this work possible. Jochen defined the state of the art of microkernel design for nearly a decade. We thank him for his support and try to continue the work in his spirit.

Helpful contributions for improving this reference manual and the L4 interface came from many persons, in particular from Alan Au, Marcus Brinkmann, Philip Derrin, Kevin Elphinstone, Bryan Ford, Andreas Haeberlen, Hermann Härtig, Gernot Heiser, Michael Hohmuth, Trent Jaeger, Ben Leslie, Jork Löser, Frank Mehnert, Yoonho Park, Marc Salem, Carl van Schaik, Sebastian Schönberg, Cristan Szmajda, Harvey Tuch, Marcus Völp, Neal Walfield, Adam Wiggins, Simon Winwood, and Jean Wolter.

# **Document History**

| draft by Jochen Liedtke | ??/?? - 06/01 |

|-------------------------|---------------|

| review by L4Ka Team     | 06/01 - 09/01 |

| L4 developers review    | Q4/01         |

| release                 | 01/02         |

viii ABOUT THIS MANUAL

# **Understanding This Document**

This L4 Reference Manual defines the generic API for all 32-bit and 64-bit machines. As such, the generic reference manual is independent of specific processor architectures. It is complemented by processor-specific ABI specifications. Some of them can be found in the appendix of this document.

In this document, we differentiate between Logical Interface, Generic Binary Interface, Generic Programming Interface, Convenience Programming Interface and Processor-specific Binary Interface.

Logical Interface The logical interface defines all concepts and logical objects such as system-call operations, logical data objects, data types and their semantics. Altogether, they form the logical L4 API.

#### Generic Binary Interface

Binary representations of most data types and generic data objects are defined independently of specific processors (although there are two different versions, one for 32-bit and a second one for 64-bit processors). Both versions together form the generic binary interface of L4.

From a purist point of view, logical interface plus generic binary interface could be regarded as a complete specification of the hardware-independent L4 microkernel interface. However, for ease-of-use and standardization reasons, the mentioned two fundamental interfaces are complemented by two more interface classes:

## Generic Programming Interface

The generic programming interface defines the objects of the logical interface and the generic binary interface as pseudo C++ classes. The language binding for regular C is for the most part identical to C++. For the cases where the C language causes function naming conflicts, the C version of the function name is given in brackets.

For the time being, only the C and C++ versions of the API are specified. The concrete syntax of other language interfaces will be left open. Later on, all language bindings will be included in the generic programming interface.

#### Convenience Programming Interface

This interface is not part of the L4 microkernel specification in the strict sense. All of its data types and procedures can be implemented using the generic programming interface. Strictly speaking, it is an interface on top of the microkernel that makes the most common operations more easily usable for the programmer.

It is important to understand that convenience and ease-of-use, not completeness, is the criterion for this interface. The convenience programming interface supports programmers by offering operations that together cover about 95% of the required microkernel functionality. For the remaining 5%, the programmer has to use the basic (not so convenient) operations of the generic programming interface.

Obviously, the convenience programming interface is not mandatory. Consequently, from a minimalist point of view, there is no need to include it in the generic L4 specification.

Nevertheless, for reasons of standardization and thus portability of software, every complete L4 language binding has to include the entire convenience programming interface.

Implementation remark: Although the convenience interface can be completely implemented on top of the generic programming interface, i.e., processor independently, the implementor of the convenience interface may implement it hardware-dependently and thus incorporate any optimization that becomes possible through a specific processor-specific binary interface.

The last interface class is not part of the generic L4 API specification.

# Processor-specific Binary Interface

Defines the processor-specific binary interface.

ABOUT THIS MANUAL ix

# **Notation**

# **Basic Data Types**

This reference manual describes the L4 API and ABI for both 32-bit and 64-bit processors. The data type Word denotes a 32-bit unsigned integer on a 32-bit processor and a 64-bit unsigned integer on a 64-bit processor. Word64, Word32, and Word16 denote 64, 32, and 16-bit words independent of the processor type.

# **Privileged Threads**

Some system calls can only be executed by privileged threads. Any thread belonging to the same address space as one of the initial threads created by the kernel upon boot-time (see page 86) are treated as privileged.

#### **Bit Fields**

Bit-field lengths are denoted as subscripts (i/j) where i relates to a 32-bit processor and j to a 64-bit processor. Bit-field subscripts (i) specify bit fields that have the same size for both 32-bit and 64-bit processors. Byte offsets are given as  $\pm i/\pm j$  for 32-bit and 64-bit processors. If all bit-fields of a specified word only add up to 32 bits, the remaining upper 32 bits on 64-bit processors are *undefined* or *ignored*.

# Undefined, Ignored, and Unchanged

| ~ | Output parameters or bit fields can be <i>undefined</i> . Corresponding parameters or fields are denoted by $\sim$ . They have no defined value on output, i.e., they may have any value or may even be inaccessible. Any algorithm relying on the value of undefined parameters or bit fields is defined to be incorrect. + No covert channel.                               |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _ | Input parameters or bit fields can be specified as <i>ignored</i> , denoted by –. Such parameters or fields can hold any value without affecting the invoked service. – is also used to define bit fields that are available for additional information. For example, fpage denotations contain some ignored bits that are used for access control bits in some system calls. |

|   | In processor-specific interfaces, registers are sometimes defined to be unchanged. This is denoted by $\equiv$ .                                                                                                                                                                                                                                                              |

# **Upward Compatibility**

The following holds for future API versions and sub-versions that are specified as *upward-compatible* to the current version.

Output parameters and bit fields.

Fields currently defined as undefined  $(\sim)$  may be specified as defined. Such newly defined fields will only deliver additional information. They can be ignored if the system call is used exactly like specified in the current API.

Input parameters and bit fields.

Fields currently defined as ignored (–) may be specified as defined. However, the content of such fields will be only relevant for newly defined features. Such fields will be ignored if a system call is used with the "old" semantics specified in this API.

x ABOUT THIS MANUAL

# **Using the API**

# **Naming**

A programmer can use all function, type, and constant definitions defined in the generic and convenience programming interfaces throughout this manual. All definitions must, however, be prefixed with the string "L4\_" and type names must contain the "\_t" suffix (e.g., use "L4\_Ipc ()" and "L4\_MsgTag\_t" rather than "Ipc ()" and "MsgTag"). The interfaces are currently only defined for C++ and C. In some cases the naming used for function names causes conflicts in the C language. These conflicts must be resolved using the alternative name specified in brackets after the function definition.

# **Include Files**

The relevant include files containing the required definitions and declarations are specified in the beginning of the generic and convenience interface sections. In general there is one include file for each chapter in the manual. If only the basic L4 data types are needed they can be included using <14/types.h>.

ABOUT THIS MANUAL xi

# **Revision History**

#### **Revision 1**

Intial revision.

# **Revision 2**

- Clarified the specification of the kernel-interface page and kernel configuration page magic.

- UntypedWords and StringItems Acceptor constants collided with function UntypedWords(MsgTag) and StringItems(MsgTag) function declaration. Renamed to UntypedWordsAcceptor and StringItemsAcceptor.

- Changed kernel ids for L4Ka kernels.

- Fixed return types for operators on the Time type.

- Changed wrx access rights in fpages to rwx. Also changed WRX reference bits in fpages returned from UNMAP system call to RWX.

- Renamed Put functions operating on MsgBuffer to Append.

- Address space deletion is now performed by deleting the last thread of an AS. This makes creation and deletion symmetrical (via ThreadControl). Before, all threads but the last were deleted by ThreadControl, and the last by SpaceControl.

- Added functions for creating ThreadIDs and for retrieving version and thread numbers from them. Fixed size of MyLocalId and MyGlobalId TCRs.

- Specified that the first three thread version numbers available for user threads are dedicated to  $\sigma_0$ ,  $\sigma_1$ , and root task respectively.

- Changed the encoding of  $\mu$  in the magic field of the KIP back to 0xE6 to be compatible with previous versions of the kernel

- Changed memory descriptors (e.g., dedicated memory) in the kernel-interface page and kernel configuration page to

use an array of typed descriptors instead of a static number of predefined ones.

- Added an appendix for the PowerPC interface.

- Added Niltag MsgTag constant.

- Decreased size of MsgBuffer structure to 32.

- Changed single Fpage& argument of Unmap() and Flush() into pass by value.

- Changed the ia32 kernel feature string "small" to "smallspaces".

- Added appendix for the ia64 interface.

- Changed the ia32 IPC and LIPC ABI to be better suitable for common hardware featuring sysenter/sysexit and gcc.

- Added ProcDesc convenience functions.

- Specified which include files to use for the various parts of the API.

- Allow privileged threads to access ia 32 Model-Specific Registers.

- Changed the ia64 ABI for system-call links and the IPC and LIPC system-calls.

- The UTCB location of a new thread is now explicitly specified by a parameter to the THREADCONTROL system-call.

- Added C versions of conflicting function names.

xii ABOUT THIS MANUAL

Added a number of convenience functions for fpages, map items, grant items, string items and kernel interface page fields.

- Added description of the send base in map and grant items.

- Changed subversion numbering for Version X.2 and Version 4 API.

- Renamed the XferTimeout TCR to XferTimeouts and split into separate send and receive timeouts.

- Added two thread specific words to each the architecture specific TCR sections. These words are free to be used by, e.g., IDL compilers.

- Changed name of L4Ka kernels to the official name. Added L4Ka::Strawberry.

- Added appendices for Alpha and MIPS64.

## **Revision 3**

- Clarified description of the *supplier* field in the kernel-interface page.

- Added NumMemoryDescriptors() convenience function.

- Clarified the return value of MemoryDescType() function.

- Fixed faulty specification of Wait\_Timeout() and ReplyWait\_Timeout().

- Added a new h-flag to control parameter in the EXCHANGEREGISTERS system-call. The h-flag controls whether the

resume/halt flag should be ignored or not.

- Changed parameter type of TimePeriod() from "int" to "Word64".

- Fixed typo in specification of the MsgTag input/output IPC parameter.

- Added comment to IPC system-call about the read-once semantics of message registers.

- Added member name "raw" to all L4 types declared as structs.

- Renamed start() and stop() functions to Start() and Stop().

- Describe semantics of undefined UTCB memory regions.

- The first 10 message registers on PowerPC are now defined as backed by physical registers.

- The first 9 message registers on Alpha are now defined as backed by physical registers.

- Fixed MR<sub>0</sub> register allocation for IA32 syscalls and adapted syscalls accordingly.

# **Revision 4**

- Added appendix for AMD64.

- Changed MIPS64 IPC ABI to include 9 message registers.

- Added SYSTEMCLOCK syscall for MIPS64.

- Clarified the fact that an interrupt thread may be the originator thread during IPC propagation.

- Added appendix for SPARC v9.

- The *high* field of memory descriptors now specifies the last addressable byte in the memory region.

ABOUT THIS MANUAL xiii

## **Revision 5**

- The ErrorCode TCR is now a generic placeholder for error descriptions of failed system-calls.

- MEMORYCONTROL now returns a result parameter.

- Defined error codes for various system-calls (EXCHANGEREGISTERS, THREADCONTROL, SCHEDULE, SPACECONTROL, PROCESSORCONTROL and MEMORYCONTROL).

- Defined convenience definitons for error code values.

- Changed the IA32 SYSTEMCLOCK ABI to clobber the EDI register.

- Specify that the KIP area and the UTCB area of an address space must not overlap.

- For the PowerPC system call trap exception IPC, use a message label of -5, and preserve register LR.

- The EXCHANGEREGISTERS system-call can no longer activate an inactive thread.

- The Fpage argument to Set\_Rights() is now passed by reference.

- Fixed inconsistencies about the number of available buffer registers.

- Renamed Void to void, Char to char, and bool to Bool.

- The Start() convenience function now aborts any ongoing IPC operations.

- The Unmap() and Flush() convenience functions operating on a single fpage now deliver the status bits of the modified fpage.

- MIPS64 now uses the k0 (\$26) register for holding the UTCB address.

- Added two new memory types for MEMORYCONTROL on MIPS64.

- Added appendix for generic BootInfo.

- Make it clear that it is not possible to activate a thread in an address space which has not been properly configured with SPACECONTROL.

- Added appendix for ARM.

- If using a 64 bit kernel, define second 32 bit word of kernel interface page to 0.

- Changed the ABI for the PowerPC system calls UNMAP and MEMORYCONTROL .

# **Revision 6**

- Removed control parameter from PROCESSORCONTROL system call binding and from the PROCESSORCONTROL Alpha system call ABI.

- Added delivery parameter to EXCHANGEREGISTERS controlling whether the syscall should deliver the thread's old values or not. Targeted at MP systems.

- Added operators for adding and subtracting two Clock values.

- Specified that  $\sigma_0$  also understands the pagefault protocol, and that anonymous  $\sigma_0$  requests will only regard conventional memory as available.

- Added ARM general exception IPC message format.

- Changes MIPS64 syscall exception IPC message format to closer match the general exception message format.

- Clarified order of IPC send and receive.

- Changed the AMD64 and IA32 specific IO port mapping interface. The kernel now uses a custom pagefault label to propagate IO pagefaults to the pager.

- Updated valid encodings for API Version, Kernel Id, and Supplier in the kernel-interface page.

- Make it clear on which processor a new thread starts executing.

xiv ABOUT THIS MANUAL

- ProcessorNo now returns a word rather than int.

- Added functions for reading IO fpages. Fixed include path for using IO fpages.

- Define that the SCHEDULE system call is also allowed if the calling thread resides in same address space as the destination thread.

Redefine values for IA32 memory attributes to better correspond with the architecture's default Page Attribute Table (PAT) values.

# **Chapter 1**

# Basic Kernel Interface

# 1.1 Kernel Interface Page [Data Structure]

2

The kernel-interface page contains API and kernel version data, system descriptors including memory descriptors, and system-call links. The remainder of the page is undefined.

The page is a microkernel object. It is directly mapped through the microkernel into each address space upon address-space creation. It is *not* mapped by a pager, can *not* be mapped or granted to another address space and can *not* be unmapped. The creator of a new address space can specify the address where the kernel interface page has to be mapped. This address will remain constant through the lifetime of that address space. Any thread can obtain the address of the kernel interface page through the KERNELINTERFACE system call (see page 7).

|                      | L4 versi              | on parts               |                                     |             |

|----------------------|-----------------------|------------------------|-------------------------------------|-------------|

| Supplier             | KernelVer             | KernelGenDate          | KernelId                            | KernDescPtı |

|                      |                       |                        |                                     | 7           |

|                      |                       | InternalFreq           | ExternalFreq                        | ProcDescPtr |

|                      |                       | Memoi                  | ·yDesc                              | MemDescPtr  |

|                      |                       |                        | <u></u>                             | ]           |

| ~                    | SCHEDULE SC           | ThreadSwitch <i>SC</i> | SystemClock SC                      | +F0 / +1E0  |

| EXCHANGEREGISTERS SC | Unmap <i>SC</i>       | Lipc <i>SC</i>         | IPC SC                              | +E0 / +1C0  |

| MEMORYCONTROL pSC    | PROCESSOR CONTROL pSC | THREADCONTROL pSC      | SPACECONTROL pSC                    | +D0/+1A0    |

| ProcessorInfo        | PageInfo              | ThreadInfo             | ClockInfo                           | +C0 / +180  |

| ProcDescPtr          | BootInfo              | ^                      | J                                   | +B0 / +160  |

| KipAreaInfo          | UtcbInfo              | ^                      | J                                   | +A0 / +140  |

|                      | ^                     | J                      |                                     | +90 / +120  |

|                      | ^                     | J                      |                                     | +80 / +100  |

|                      | ^                     | J                      |                                     | +70 / +E0   |

|                      |                       | J                      |                                     | +60 / +C0   |

| •                    | V                     | MemoryInfo             | ~                                   | +50 / +A0   |

|                      | ^                     | J                      |                                     | +40 / +80   |

|                      | ^                     | J                      |                                     | +30 / +60   |

|                      | ^                     | J                      |                                     | +20 / +40   |

|                      | ^                     |                        |                                     | +10 / +20   |

| KernDescPtr          | API Flags             | API Version            | 0 <sub>(0/32)</sub> 'K' 230 '4' 'L' | +0          |

| +C / +18             | +8 / +10              | +4 / +8                | +0                                  |             |

Note that this kernel interface page is basically upward compatible to the *kernel info page* of versions 2 and X.0. The magic byte string "L4 $\mu$ K" at the beginning of the object identifies the kernel interface page.

**Version/id number convention:** Version/subversion/subsubversion numbers and id/subid numbers with the most significant bit 0 denote official versions/ids and are globally unique through all suppliers. Version/id numbers that have the most significant bit set to 1 denote experimental versions/ids and may be unique only in the context of a supplier.

# **API Description**

API Version

|--|

| version | subversion |                                         |

|---------|------------|-----------------------------------------|

| 0x02    |            | Version 2                               |

| 0x83    | 0x80       | Experimental Version X.0                |

| 0x83    | 0x81       | Experimental Version X.1                |

| 0x84    | rev        | Experimental Version X.2 (Revision rev) |

| 0x85    |            | Dresden L4.Sec                          |

| 0x86    | rev        | NICTA N1 (Revision rev)                 |

| 0x04    | rev        | Version 4 (Revision rev)                |

**API Flags**

ee = 00 : little endian, = 01 : big endian.

00 00 11 17

ww = 00 : 32-bit API, = 01 : 64-bit API.

Note that this field can not be used directly to differentiate between little endian and big endian mode since the ee field resides in different bytes for both modes. Furthermore, the offset address of the API Flags is different for 32-bit and 64-bit modes. In summary, a direct inspection of the kernel interface page is not sufficient to securely differentiate between 32/64-bit modes and little/big endian modes.

Secure mode detection is enabled through the KERNELINTERFACE system call (see page 7). It delivers the API Flags in a register.

# System Description

**ProcessorInfo**

s

| $rs - 1_{(16)}$ |

|-----------------|

|                 |

The size of the area occupied by a single processor description is  $2^s$ . Location of description fields for the first processor is denoted by ProcDescPtr. Description fields for subsequent processors are located directly following the previous one.

processors

Number of available system processors.

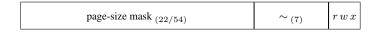

**PageInfo**

page-size mask

If bit k-10 of the page-size mask field (bit k of the entire word) is set to 1 hardware and kernel support pages of size  $2^k$ . If the bit is 0 hardware and/or kernel do not support pages of size  $2^k$ . Note that fpages of size  $2^k$  can be used, even if  $2^k$  is no supported hardware page size. Information about supported hardware page sizes is only a performance hint.

rwx

Identifies the supported access rights (read, write, execute) that can be set independently of other access rights. A 1-bit signals that the right can be set and reset on a mapped page. For rwx = 010, only write permission could be controlled orthogonally. The processor would implicitly permit read and execute access on any mapped page. For rwx = 111, all three rights could be set and reset independently.

## ThreadInfo

| $UserBase_{\ (12)}$ | $SystemBase\ _{(12)}$ | t (8) |

|---------------------|-----------------------|-------|

|---------------------|-----------------------|-------|

Number of valid thread-number bits. The thread number field may be larger but only bits  $0 \dots t - 1$  are significant for this kernel. Higher bits must all be 0.

#### UserBase

Lowest thread number available for user threads (see page 14). The first three thread numbers will be used for the initial thread of  $\sigma_0$ ,  $\sigma_1$ , and root task respectively (see page 86). The version numbers (see page 14) for these initial threads will equal to one.

#### SystemBase

Lowest thread number used for system threads (see page 14). Thread numbers below this value denote hardware interrupts.

#### ClockInfo

| SchedulePrecision (16) | ReadPrecision (16) |

|------------------------|--------------------|

|------------------------|--------------------|

# ReadPrecision

Specifies the minimal time difference  $\neq 0$  that can be detected by reading the system clock through the SYSTEMCLOCK system call. Basically, this is the precision of the system clock when reading it.

#### SchedulePrecision

Specifies the maximal jitter  $(\pm)$  for a scheduled thread activation based on a wakeup time (provided that no thread of higher or equal priority is active and timer interrupts are enabled). Precisions are given as time periods (see page 28).

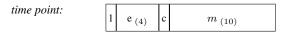

# UtcbInfo

| $m_{(10)}$ |

|------------|

|            |

- The minimal area size for an address space's UTCB area is  $2^s$ . The size of the UTCB area limits the total number of threads k to  $2^a mk \le 2^s$ .

- m UTCB size multiplier.

- The UTCB location must be aligned to  $2^a$ . The total size required for one UTCB is  $2^a m$ .

# ${\it KipAreaInfo}$

s The size of the kernel interface page area is  $2^s$ .

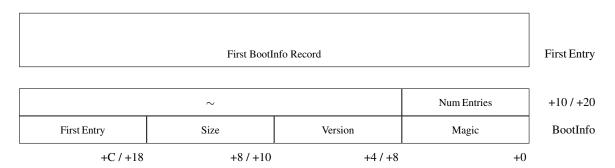

## BootInfo

Prior to kernel initialization a boot loader can write an arbitrary value into the BootInfo field of the kernel configuration page (see page 86). Post-initialization code, e.g., a root server can later read the field from the kernel interface page. Its value is neither changed nor interpreted by the kernel. This is a generic method for passing system information across kernel initialization.

# **Processor Description**

ProcDescPtr

Points to an array containing a description for each system processor. The *ProcessorInfo* field contains the dimension of the array. *ProcDescPtr* is given as an address relative to the kernel interface page's base address.

ExternalFreq Extern

External Bus frequency in kHz.

*InternalFreq*

Internal processor frequency in kHz.

# **Kernel Description**

**KernDescPtr**

Points to a region that contains 4 kernel-version words (see below) followed by a number of 0-terminated plaintext strings. The first plaintext string identifies the current kernel followed by further optional kernel-specific versioning information. The remaining plaintext strings identify architecture dependent kernel features (see Appendix A.3). A zero length string (i.e., a string containing only a 0-character) terminates the list of feature descriptions.

KernelDescPtr is given as an address relative to the kernel interface page's base address.

KernelId

Can be used to identify the microkernel.

| id | subid | kernel                    | supplier         |

|----|-------|---------------------------|------------------|

| 0  | 1     | L4/486                    | GMD              |

| 0  | 2     | L4/Pentium                | IBM              |

| 0  | 3     | L4/x86                    | UKa              |

| 1  | 1     | L4/Mips                   | UNSW             |

| 2  | 1     | L4/Alpha                  | TUD, UNSW        |

| 3  | 1     | Fiasco                    | TUD              |

| 4  | 1     | L4Ka::Hazelnut            | UKa              |

| 4  | 2     | L4Ka::Pistachio           | UKa, UNSW, NICTA |

| 4  | 3     | L4Ka::Strawberry          | UKa              |

| 5  | 1     | NICTA::Pistachio-embedded | NICTA            |

KernelGenDate

Kernel generation date.

KernelVer

| ver (8) | subver (8) | subsubver (16) |

|---------|------------|----------------|

Can be used to identify the microkernel version. Note that this kernel version is not necessarily related to the API version.

Supplier

The four least significant bytes of the supplier field specify a character string identifying the kernel supplier:

"GMD<sub>\_</sub>" "IBM<sub>\_</sub>" **GMD**

IBM Research

"UNSW" University of New South Wales, Sydney

"TUD\_" Technische Universität Dresden "UKa\_" Universität Karlsruhe (TH) "NICT" National ICT Australia (NICTA)

# System-Call Links

pSC

SCLink for normal system call.

> Link for privileged system call, i.e., a system call that can only be performed by a privileged thread.

> The system-call links specify how the application can invoke system-calls for the current microkernel. The interpretation of the system-call links is ABI specific, but will typically be addresses relative to the kernel interface page's base address where kernel provided system-call stubs are located.

# **Memory Description**

# MemoryInfo

6

| MemDescPtr (16/32) | $n_{\ (16/32)}$ |

|--------------------|-----------------|

|--------------------|-----------------|

# MemDescPtr

Location of first memory descriptor (as an offset relative to the kernel-interface page's base address). Subsequent memory descriptors are located directly following the first one. For memory descriptors that specify overlapping memory regions, later descriptors take precedence over earlier ones.

*n* Number of memory descriptors.

# MemoryDesc

| $high/2^{10}~_{(22/54)}$ |   | ~ (10) |       | +4 / +8  |    |

|--------------------------|---|--------|-------|----------|----|

| $low/2^{10}$ (22/54)     | v | ~      | t (4) | type (4) | +0 |

high Address of last byte in memory region. The ten least significant address bits are all hardwired to 1.

low Address of first byte in memory region. The ten least significant address bits are all hardwired to 0.

Indicates whether memory descriptor refers to physical memory (v=0) or virtual memory (v=1).

type Identifies the type of the memory descriptor.

| Description                                           |

|-------------------------------------------------------|

| Undefined                                             |

| Conventional memory                                   |

| Reserved memory (i.e., reserved by kernel)            |

| Dedicated memory (i.e., memory not available to user) |

| Shared memory (i.e., available to all users)          |

| Defined by boot loader                                |

| Architecture dependent                                |

|                                                       |

# t, type = 0xE

The type of the memory descriptor is dependent on the bootloader. The t field specifies the exact semantics. Refer to boot loader specification for more info.

# t, type = 0xF

The type of the memory descriptor is architecture dependent. The t field specifies the exact semantics. Refer to architecture specific part for more info (see page 117).

# t, $type \neq 0xE$ , $type \neq 0xF$

The type of the memory descriptor is solely defined by the type field. The content of the t field is undefined.

# 1.2 KERNELINTERFACE [Slow Systemcall]

→ void\* kernel interface page

Word API Version

Word API Flags

Word KernelId

Delivers base address of the *kernel interface page*, *API version*, and *API flags*. The latter two values are copies of the corresponding fields in the kernel interface page. The API information is delivered in registers through this system call (a) to enable unrestricted structural changes of the kernel interface page in future versions, and (b) to enable secure detection of the kernel's endian mode (little/big) and word width (32/64).

The structure of the *kernel interface page* is described on page 2. The page is a microkernel object. It is directly mapped through the microkernel into each address space upon address-space creation. It is *not* mapped by a pager, can *not* be mapped or granted to another address space and can *not* be unmapped. The creator of a new address space can specify the address where the kernel interface page has to be mapped. This address will remain constant through the lifetime of that address space.

Any thread can determine the address of the kernel interface page through this system call. Since the system call may be slow it is highly recommended to store the address in a static variable for further use.

It is also possible to use a unique address for the kernel interface page in all address spaces of a (sub)system. Then, the kernel interface page can be accessed by fixed absolute addresses without using the current system call.

Besides other things, the page describes the current API, ABI, and microkernel version so that a server or an application can find out whether and how it can run on the current microkernel. Since the kernel interface page also contains API-and ABI-specific data for most other system calls the page's base address is typically required before any other system call can be used.

To enable version detection independently of the API and ABI, the current system call is guaranteed to work in all L4 versions. The systemcall code will never change and will be the same on compatible processors. (If a processor is upward compatible to multiple incompatible processors the kernel should offer multiple systemcall codes for this function.)

# **Output Parameters** kernel interface page Ver X.1 and above base address (32/64) Kernel interface page address, always page aligned. 0 is no valid address. Ver X.0 and below $0_{(32/64)}$ Older versions (2, X.0, etc.) do not include the kernel interface page as a kernel mapped page. No address is delivered. **API Version** version (8) subversion (8) $\sim$ (16) see page 3, "Kernel Interface Page" **API Flags** wwee $\sim$ (28/60) see page 3, "Kernel Interface Page"

KernelId

| id (8) subid (8) | ~ (16) |

|------------------|--------|

|------------------|--------|

see page 5, "Kernel Interface Page"

# **Pagefaults**

No pagefaults will happen.

# **Generic Programming Interface**

# **System-Call Function:**

```

#include <l4/kip.h>

```

void \* KernelInterface (Word& ApiVersion, ApiFlags, KernelId)

Word ThreadIdBits (void\* KernelInterface)

$Word \ \textit{ThreadIdSystemBase} \ \ (void*KernelInterface)$

# **Convenience Programming Interface**

#### **Derived Functions:**

```

#include <I4/kip.h>

struct MEMORYDESC { Word raw [2] }

struct PROCDESC { Word raw [4] }

void* KernelInterface ()

[GetKernelInterface]

Delivers a pointer to the kernel interface page.

Word ApiVersion ()

Word ApiFlags ()

Word KernelId ()

void KernelGenDate (void* KernelInterface, Word& year, month, day)

Word KernelVersion (void* KernelInterface)

Word KernelSupplier (void* KernelInterface)

Delivers the API Version/API Flags/Kernel Id/kernel generation date/kernel version/kernel sup-

plier.

Word NumProcessors (void* KernelInterface)

Word NumMemoryDescriptors (void* KernelInterface)

Delivers number of processors in the system/number of memory descriptors in the kernel-

interface page.

Word PageSizeMask (void* KernelInterface)

Word PageRights (void* KernelInterface)

```

Delivers supported page sizes/page rights for the current kernel/hardware architecture.

Word ThreadIdUserBase (void\* KernelInterface)

Delivers number of valid bits for thread numbers/lowest thread number for system threads/lowest thread number for user threads.

Word ReadPrecision (void\* KernelInterface)

Word SchedulePrecision (void\* KernelInterface)

Delivers the SYSTEMCLOCK read precision/maximal jitter for wakeups (both in  $\mu$ s).

Word UtcbAreaSizeLog2 (void\* KernelInterface)

Word UtcbAlignmentLog2 (void\* KernelInterface)

Word UtcbSize (void\* KernelInterface)

Delivers required minimum size of UTCB area/alignment requirement for UTCBs/size of a single UTCB.

Word KipAreaSizeLog2 (void\* KernelInterface)

Delivers size of kernel interface page area.

Word **BootInfo** (void\* KernelInterface)

Delivers the contents of the boot info field.

char\* KernelVersionString (void\* KernelInterface)

Delivers the kernel version string.

char\* Feature (void\* KernelInterface, Word num)

Delivers the numth kernel feature string, or a null pointer if num exceeds the number of available feature strings.

MemoryDesc\* MemoryDesc (void\* KernelInterface, Word num)

Delivers the numth memory descriptor, or a null pointer if num exceeds the number of available descriptors.

ProcDesc\* ProcDesc (void\* KernelInterface, Word num)

Delivers the numth processor descriptor, or a null pointer if num exceeds the number of processors of the system (see ProcessorInfo).

# **Support Functions:**

#include <I4/kip.h>

Word UndefinedMemoryType

Word Conventional Memory Type

Word ReservedMemoryType

Word DedicatedMemoryType

Word SharedMemoryType

Word BootLoaderSpecificMemoryType

Word ArchitectureSpecificMemoryType

Bool IsVirtual (MemoryDesc& m)

[IsMemoryDescVirtual]

Delivers true if memory descriptor specifies a virtual memory region.

Word **Type** (MemoryDesc& m)

[MemoryDescType]

Word **Low** (MemoryDesc& m)

[MemoryDescLow]

Word **High** (MemoryDesc& m)

[MemoryDescHigh]

Delivers type (t\*16 + type), low limit, and high limit of memory region.

$\label{eq:word_externalFreq} Word_{\begin{subarray}{c} \begin{subarray}{c} \begin{su$

[ProcDescExternalFreq]

[ProcDescInternalFreq]

VIRTUAL REGISTERS 11

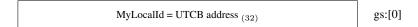

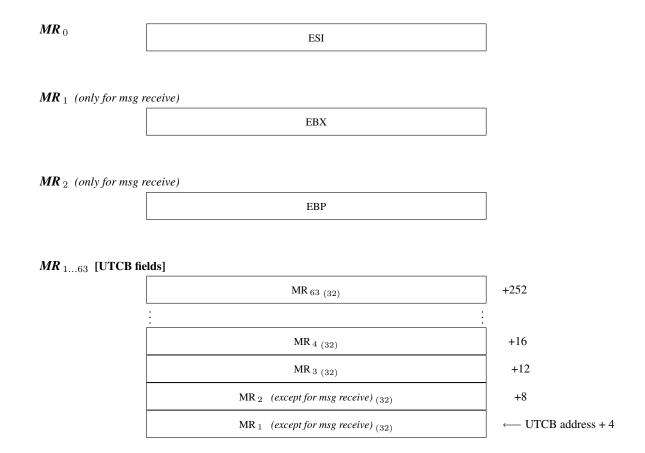

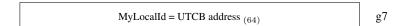

# 1.3 Virtual Registers [Virtual Registers]

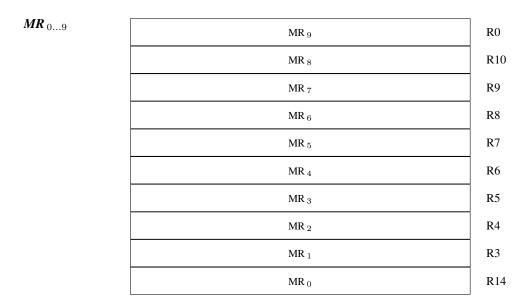

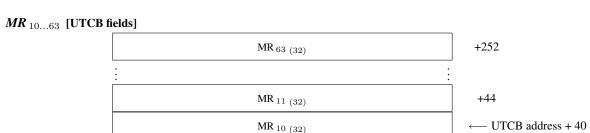

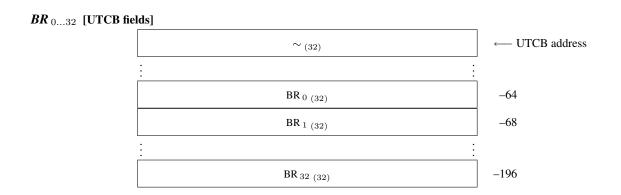

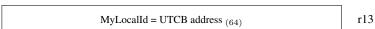

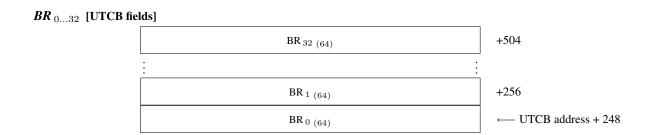

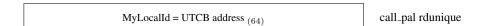

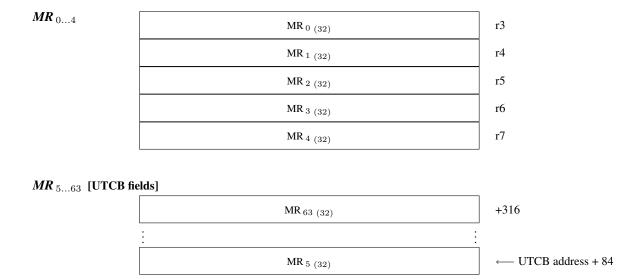

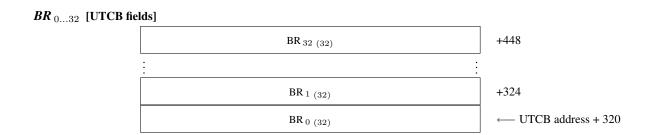

Virtual registers are implemented by the microkernel. They offer a fast interface to exchange data between the microkernel and user threads. Virtual registers are *registers* in the sense that they are static per-thread objects. Dependent on the specific processor type, they can be mapped to hardware registers or to memory locations. Mixtures, some virtual registers to hardware registers, some to memory are also possible. The ABI for virtual-register access depends on the specific processor type and on the virtual-register type, see Appendices A.1, B.1 and C.1 for specific hardware details.

There are three classes of virtual registers:

- Thread Control Registers (TCRs), see page 16

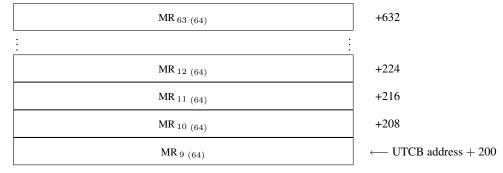

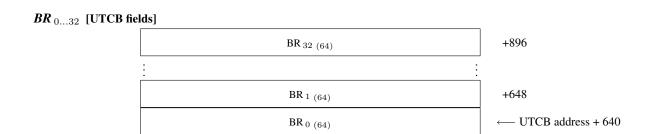

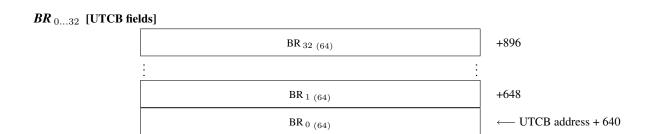

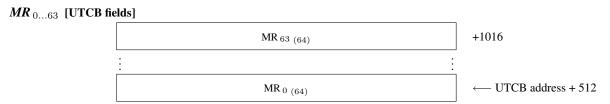

- Message Registers (MRs), see page 48

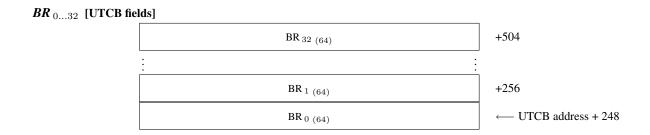

- Buffer Registers (BRs), see page 59

Loading illegal values into virtual registers, overwriting read-only virtual registers, or accessing virtual registers of other threads in the same address space (which may be physically possible if some are mapped to memory locations) is illegal and can have undefined effects on all threads of the current address space. However, since virtual registers can *not* be accessed across address spaces, they are safe from the kernel's point of view: Illegal accesses can like any other programming bug only compromise the originator's address space.

Remark:

In general, virtual registers can only be addressed directly, not indirectly through pointers. The generic API therefore offers no operations for indirect virtual-register access. However, processor-specific code generators might use indirect access techniques if the ABI permits it.

# **Generic Programming Interface**

```

#include <|4/message.h>

void StoreMR (int i, Word& w)

void LoadMR (int i, Word w)

Delivers/sets MR _i.

void StoreMRs (int i, k, Word& [k] w)

void LoadMRs (int i, k, Word& [k] w)

Stores/loads MR _{i...i+k-1} to/from memory.

void StoreBR (int i, Word& w)

void LoadBR (int i, Word w)

Delivers/sets the value of BR _i.

void StoreBRs (int i, k, Word& [k])

void LoadBRs (int i, k, Word& [k])

Stores/loads BR _{i...i+k-1} to/from memory.

```

12 VIRTUAL REGISTERS

# **Chapter 2**

# Threads

14 THREADID

# 2.1 ThreadId [Data Type]

Thread IDs identify threads and hardware interrupts. A thread ID can be *global* or *local*. Global thread IDs are unique through the entire system. They identify threads independently of the address space in which they are used. Local thread IDs exist per address space; the scope of a thread's local ID is only the thread's own address space. In different address spaces, the same local thread ID may identify different and unrelated threads.

Note that any thread has a global and a local thread ID. Both global and local thread IDs are encoded in a single word.

#### **Global Thread ID**

A global thread ID consists of a word, where 18 bits (32-bit processor) or 32 bits (64-bit processor) determine the thread number and 14 bits (32-bit processor) or 32 bits (64-bit processor) are available for a version number. At least one of the lowermost 6 version bits must be 1 to differentiate a global from a local thread ID.

User-thread numbers can be freely allocated within the interval [UserBase,  $2^t$ ), where t denotes the upper limit of thread IDs. The thread-number interval [SystemBase, UserBase) is reserved for L4-internal threads. Hardware interrupts are regarded as hardware-implemented threads. Consequently, they are identified by thread IDs. Their corresponding thread numbers are within the interval [0, SystemBase). The values SystemBase, UserBase, and t are published in the kernel interface page (see page 4).

| global thread ID    | thread no $(18/32)$        | $version_{\left(14/32\right)} \neq 0 \pmod{64}$ |  |

|---------------------|----------------------------|-------------------------------------------------|--|

| global interrupt ID | intr no <sub>(18/32)</sub> | 1 (14/32)                                       |  |

Global thread IDs have a version field whose content can be freely set by those threads that can create and delete threads. However, the lowermost 6 bits of the version must not all be 0, i.e.  $v \mod 64 \neq 0$  must hold for every version v. For hardware interrupts, the version field is always 1.

The microkernel checks version fields whenever a thread is accessed through its global thread ID. However, the semantics of the version field are not defined by the microkernel. OS personalities are free to use this field for any purpose. For example, they may use it to make thread IDs unique in time.

# **Local Thread ID**

Local thread IDs identify threads within the same address space. They are identified by the 6 lowermost bits being 0.

# **Special Thread IDs**

Special IDs exist for *nilthread* and two wild cards. The thread ID *anythread* matches with any given thread ID, including all interrupt IDs. The ID *anylocalthread* matches all threads that reside in the same address space.

| nilthread      | 0 (32/64)             |        |  |

|----------------|-----------------------|--------|--|

| anythread      | $-1_{(32/64)}$        |        |  |

| anylocalthread | <sup>-1</sup> (26/58) | 000000 |  |

THREADID 15

# **Generic Programming Interface**

```

#include <|4/thread.h>

struct ThreadId Nord raw }

ThreadId nilthread

ThreadId anythread

ThreadId anylocalthread

ThreadId GlobalId (Word threadno, version)

Delivers a thread ID with indicated thread and version number.

Word Version (ThreadId t)

Word ThreadNo (ThreadId t)

Delivers version/thread number of indicated global thread ID.

```

# **Convenience Programming Interface**

```

#include <l4/thread.h>

Bool == (ThreadId \ l, \ r)

[IsThreadEqual]

Bool != (ThreadId l, r)

[IsThreadNotEqual]

Check if thread IDs match or differ. The result of comparing a local ID with a global ID will

always indicate a mismatch, even if the IDs refer to the same thread.

Bool SameThreads (ThreadId l, r)

\{ GlobalId (l) == GlobalId (r) \}

Check if thread IDs refer to the same thread. Also works if one ID is local and the other is

Bool IsNilThread (ThreadId t)

\{ t == nilthread \}

Bool IsLocalId (ThreadId t)

Bool IsGlobalId (ThreadId t)

Check if thread ID is a local/global one.

ThreadId LocalId (ThreadId t)

[LocalIdOf]

ThreadId GlobalId (ThreadId t)

[GlobalIdOf]

Delivers the local/global ID of the specified local thread. Specifying a non-local thread delivers

nilthread (see EXCHANGEREGISTERS, page 18).

ThreadId MyLocalId ()

ThreadId MyGlobalId ()

Delivers the local/global ID of the currently running thread (see TCRs, page 16).

ThreadId Myself ()

{ MyGlobalId () }

```

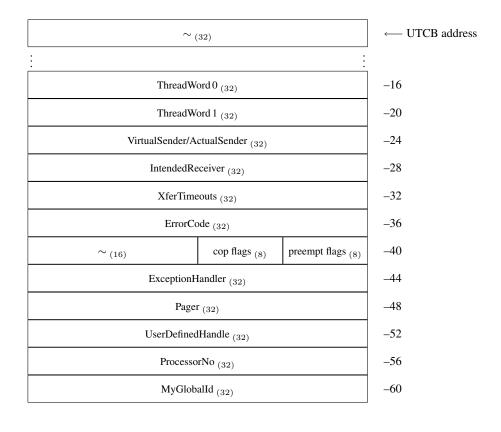

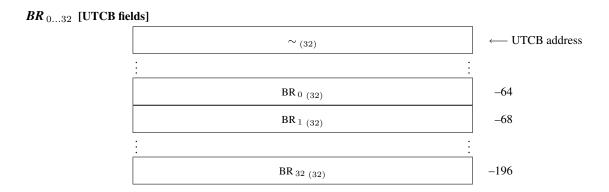

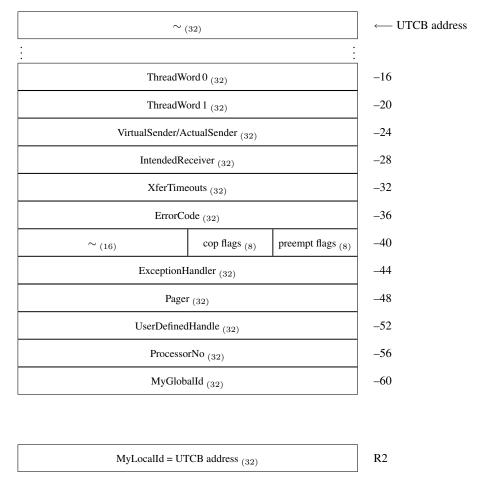

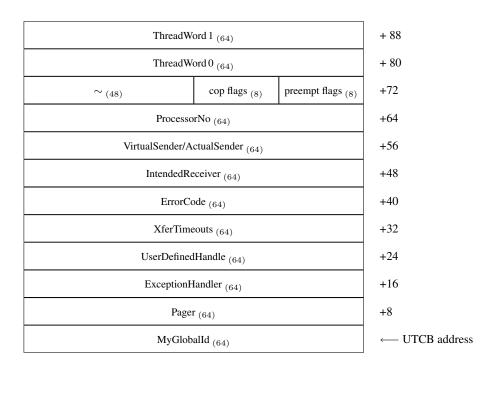

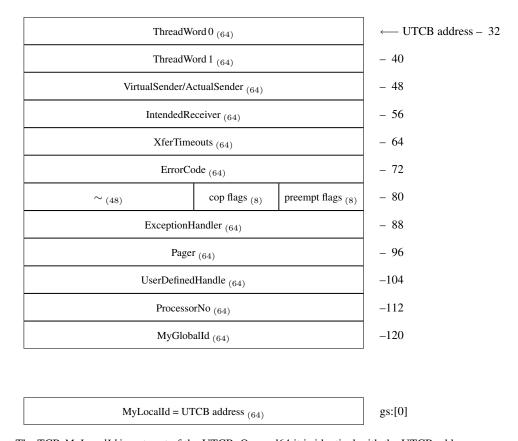

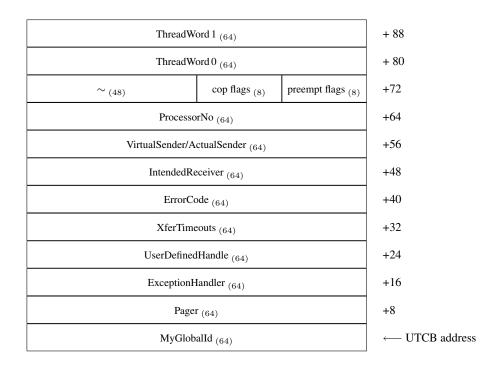

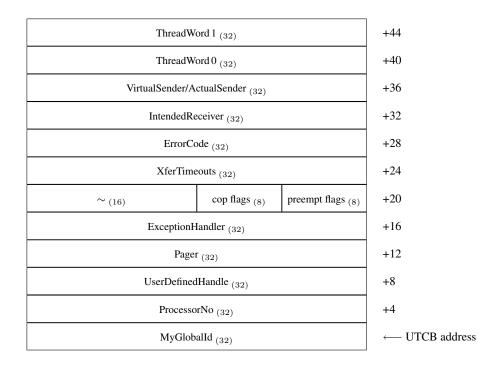

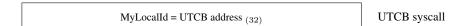

# 2.2 Thread Control Registers (TCRs) [Virtual Registers]

TCRs are a fast mechanism to exchange relatively static control information between user thread and microkernel. TCRs are static non-transient per-thread registers.

| VirtualSender/ActualSender (32/64) | R/W    | see IPC           |

|------------------------------------|--------|-------------------|

| IntendedReceiver (32/64)           | R-only | see IPC           |

| XferTimeouts (32/64)               | R/W    | see IPC           |

| ErrorCode (32/64)                  | R-only | see system-calls  |

| Preempt Flags (8)                  | R/W    | see Scheduling    |

| Cop Flags (8)                      | W-only | see Miscellaneous |

| ExceptionHandler (32/64)           | R/W    | see Miscellaneous |

| Pager (32/64)                      | R/W    | see Protocols     |

| UserDefinedHandle (32/64)          | R/W    | see Threads       |

| ProcessorNo (32/64)                | R-only | see Miscellaneous |

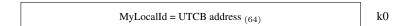

| MyLocalId (32/64)                  | R-only | see Threads, IPC  |

| MyGlobalId (32/64)                 | R-only | see Threads, IPC  |

| MyGlobalId  | Global ID of the thread.                                     |

|-------------|--------------------------------------------------------------|

| MyLocalId   | Local ID of the thread.                                      |

| ProcessorNo | The processor number on which the thread currently executes. |

# ${\it User Defined Handle}$

This field can be freely set and read by user threads. It can, e.g., be used for storing a thread number, a pointer to an additional user thread control block, etc.

# **Generic Programming Interface**

The listed generic functions permit user code to access TCRs independently of the processor-specific TCR model. All functions are user-level functions; the microkernel is not involved.

```

#include <l4/thread.h>

ThreadId MyLocalId ()

ThreadId MyGlobalId ()

Delivers the local/global ID of the currently running thread (see TCRs, page 16).

ThreadId Myself ()

{ MyGlobalId () }

Word ProcessorNo ()

Delivers the processor number the current thread is running on. Delivered value is a valid index

into the processor description array (see Kernel Interface Page, page 4).

Word UserDefinedHandle ()

void Set_UserDefinedHandle (Word NewValue)

Delivers/sets the user defined handle of the currently running thread.

ThreadId Pager ()

void Set_Pager (ThreadId NewPager)

Delivers/sets the pager for the currently running thread.

ThreadId ExceptionHandler ()

void Set_ExceptionHandler (ThreadId NewHandler)

Delivers/sets the exception handler for the currently running thread.

void Set_CopFlag (Word n)

void Clr_CopFlag (Word n)

Sets/clears coprocessor flag c_n.

Word ErrorCode ()

Delivers the error code of the last system-call.

Word XferTimeouts ()

void Set_XferTimeouts (Word NewValue)

Delivers/sets the transfer timeouts for the currently running thread (see IPC, page 63).

ThreadId IntendedReceiver ()

Delivers the intended receiver of last received IPC (see IPC, page 64).

ThreadId ActualSender ()

Delivers the actual sender of the last propagated IPC (see IPC, page 63).

void Set_VirtualSender (ThreadId t)

Sets the virtual sender for the next deceiving IPC (see IPC, page 63).

```

Code generators of IDL and other compilers are not restricted to the generic interface. They can use any processor-specific methods and optimizations to access TCRs.

#### 2.3 **EXCHANGEREGISTERS** [Systemcall]

| ThreadId | dest -            | $\longrightarrow$ | ThreadId | result            |

|----------|-------------------|-------------------|----------|-------------------|

| Word     | control           |                   | Word     | control           |

| Word     | SP                |                   | Word     | SP                |

| Word     | IP                |                   | Word     | IP                |

| Word     | FLAGS             |                   | Word     | FLAGS             |

| ThreadId | pager             |                   | ThreadId | pager             |

| Word     | UserDefinedHandle |                   | Word     | UserDefinedHandle |

Exchanges or reads a thread's FLAGS, SP, and IP hardware registers as well as pager and UserDefinedHandle TCRs. Furthermore, thread execution can be suspended or resumed. The destination thread must be an active thread (see page 22) residing in the invoker's address space.

Any IP, SP, or FLAGS modification changes the corresponding user-level registers of the addressed thread. In general, ongoing kernel activities are not influenced. However, a currently active IPC operation can be canceled or aborted. For details see the SR-bit specification below.

Modifications of the pager TCR and the UserDefinedHandle TCR become immediately effective, whether the destination thread executes in user mode or in kernel mode.

# **Input Parameters**

| A | '^ | _ | 4 |

|---|----|---|---|

|   |    |   |   |

Thread ID of the addressed thread. This may be a local or a global ID. However, the addressed

| aesi    | thread must reside in the current address space. faster in some implementations.                                                                                                                                                                                                                                                                               | ,                                             |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

| control | 0 (22/54)                                                                                                                                                                                                                                                                                                                                                      | dhpufisSRH                                    |  |

| hpufis  | The $s$ -flag refers to the $SP$ register, $i$ to $IP$ , $f$ to $FLAGS$ , $u$ to the $UserDefinedHandle$ TCR, $p$ to the $pager$ TCR, and $h$ to the $H$ -flag. If a flag is set to 1, the register/state is overwritten by the corresponding input parameter. Otherwise, the corresponding input parameter is ignored and the register/state is not modified. |                                               |  |

| SR      | Controls whether the addressed thread's ongoin through the system call or not.                                                                                                                                                                                                                                                                                 | ng IPC opereration should be canceled/aborted |  |

| S = 0   | An IPC operation of the addressed thread that is a message will continue as usual. <i>SP</i> , <i>IP</i> or <i>F</i> operation terminates.                                                                                                                                                                                                                     |                                               |  |

| S = 1   | An IPC operation of the addressed thread that canceled. An IPC operation that is currently sen                                                                                                                                                                                                                                                                 |                                               |  |

| R = 0   | An IPC operation of the addressed thread that receiving a message will continue as usual. <i>SP</i> , <i>I</i> IPC operation terminates.                                                                                                                                                                                                                       |                                               |  |

| R = 1   | An IPC operation of the addressed thread that is <i>canceled</i> . An IPC operation that is currently rec                                                                                                                                                                                                                                                      | , ,                                           |  |

| H       | Halts/resumes the thread if $h = 1$ . Ignored for $h$                                                                                                                                                                                                                                                                                                          | a = 0.                                        |  |

- H = 0No effect if the thread was not halted. Otherwise, thread execution is resumed.

- User-level thread execution is halted. Note that ongoing IPCs and other kernel operations are H = 1not affected by H. (See SR for also aborting active IPC.)

| d            | If $d=1$ the result parameters (IP, SP, FLAGS, UserDefinedHandle, pager, control) are delivered. If $d=0$ the return values are undefined.        |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SP           | The current user-level stack pointer is set to $SP$ if $s=1$ . Ignored for $s=0$ .                                                                |  |

| IP           | The current user-level instruction pointer is set to $IP$ if $i=1$ . Ignored for $i=0$ .                                                          |  |

| FLAGS        | Sets the user-level processor flags of the thread if $f=1$ . Ignored for $f=0$ . The semantics of the $FLAGS$ word depends on the processor type. |  |

| UserDefinedI | UserDefinedHandle Sets the thread's UserDefinedHandle TCR if $u=1$ . Ignored for $u=0$ .                                                          |  |

| pager        | Sets the thread's pager TCR if $p=1$ . Ignored for $p=0$ .                                                                                        |  |

# **Output Parameters**

result ≠ nilthread, input parameter dest was a local thread ID global thread ID of the addressed thread. EXCHANGEREGISTERS succeeded.

$\textit{result} \neq \textit{nilthread}, \textit{input parameter} \textit{ dest was a global thread ID}$

local thread ID of the addressed thread. EXCHANGEREGISTERS succeeded.

**result** = nilthread Operation failed. The ErrorCode TCR indicates the reason for the failure.

**ErrorCode** [TCR] Set if result = nilthread. Undefined if  $result \neq nilthread$ .

=2 Invalid thread. The *dest* parameter specified an invalid thread ID, an inactive thread, or a thread within a different address space.

| control |       | $0_{(29/61)}$ $SRH$                                                                                                                                                                                                                                                                                                                    |

|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |       | The control parameter is only valid if $d=1$ and undefined otherwise.                                                                                                                                                                                                                                                                  |

| Н       |       | Reports whether the addressed thread was halted $(H=1)$ or not $(H=0)$ when EXCHANGE-REGISTERS was invoked. Note that this output $control$ bit is independent of the input parameter $control$ .                                                                                                                                      |

| SR      |       | Reports whether the addressed thread was within an IPC operation when EXCHANGEREGISTERS was invoked. A value of 0 reports that the addressed thread was not within a send phase $(S=0)$ or not within a receive phase $(R=0)$ , respectively. Note that these output $control$ bits are independent of the input parameter $control$ . |

|         | R = 1 | Operation was executed while the addressed thread was within the receive phase of an IPC operation. Iff the input control word had $R=1$ the IPC operation was canceled or aborted.                                                                                                                                                    |

|         | S = 1 | Operation was executed while the addressed thread was within the send phase of an IPC operation. Iff the input control word had $S=1$ the IPC operation was canceled or aborted.                                                                                                                                                       |

| SP                                                                                                  | Old user-level stack pointer of the thread, if $d=1$ and undefined for $d=0$ .                                           |  |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| IP                                                                                                  | Old user-level instruction pointer of the thread, if $d=1$ and undefined for $d=0$ .                                     |  |

| FLAGS                                                                                               | Old user-level flags of the thread, if $d=1$ and undefined for $d=0$ . The semantics of this word is processor specific. |  |

| UserDefinedHandle Old content of thread's UserDefinedHandle TCR, if $d=1$ and undefined for $d=0$ . |                                                                                                                          |  |

| pager                                                                                               | Old content of thread's $pager$ TCR, if $d=1$ and undefined for $d=0$ .                                                  |  |

# **Pagefaults**

No pagefaults will happen.

# **Generic Programming Interface**

# System-Call Function:

#include < 14/thread.h>

ThreadId ExchangeRegisters (ThreadId dest, Word control, sp, ip, flags, UserDefinedHandle, ThreadId pager, Word& old\_control, old\_sp, old\_flags, old\_UserDefinedHandle, ThreadId& old\_pager)

# **Convenience Programming Interface**

# **Derived Functions:**

#include <l4/thread.h>

ThreadId GlobalId (ThreadId t) [GlobalIdOf]  $\{ \text{ if (IsLocalId (t)) ExchangeRegisters (t,0,-...) else t } \}$

Delivers global ID of specified local thread. Specifying a non-local thread delivers nilthread.

ThreadId LocalId (ThreadId t) [LocalIdOf]

$\big\{ \text{ if (IsGlobalId (t)) ExchangeRegisters (t,0,-...) else t } \big\}$

Delivers local ID of specified local thread. Specifying a non-local thread delivers nilthread.

Word UserDefinedHandle (ThreadId t) [UserDefinedHandleOf]

void **Set\_UserDefinedHandle** (ThreadId t, Word handle) [Set\_UserDefinedHandleOf]

Delivers/sets the user defined handle of specified local thread. Result of specifying a non-local thread is undefined.

ThreadId Pager (ThreadId t) [PagerOf]

void Set\_Pager (ThreadId t, p) [Set\_PagerOf]

Delivers/sets the pager for specified local thread. Result of specifying a non-local thread is undefined.

```

void Start (ThreadId t)

void Start (ThreadId t, Word sp, ip)

[Start_SpIp]

void Start (ThreadId t, Word sp, ip, flags)

[Start_SpIpFlags]

Resume execution of specified local thread (if halted). Abort any ongoing IPC operations. Op-

tionally modify stack pointer, instruction pointer, and processor flags according to function pa-

rameters. Result of specifying a non-local thread is undefined.

ThreadState Stop (ThreadId t)

ThreadState Stop (ThreadId t, Word& sp, ip, flags)

[Stop_SpIpFlags]

Halt execution of specified local thread and return its current thread state. Do not abort any on-

going IPC operation. Optionally return thread's stack pointer, instruction pointer, and processor

flags in output parameters. Result of specifying a non-local thread is undefined.

ThreadState AbortReceive_and_stop (ThreadId t)

ThreadState AbortReceive_and_stop (ThreadId t, Word& sp, ip, flags)

[AbortReceive_and_stop_SpIpFlags]

As stop (), except any ongoing IPC receive operation is immediately aborted.

ThreadState AbortSend_and_stop (ThreadId t)

ThreadState AbortSend_and_stop (ThreadId t, Word& sp, ip, flags)

[AbortSend_and_stop_SpIpFlags]

As stop (), except any ongoing IPC send operation is immediately aborted.

ThreadState AbortIpc_and_stop (ThreadId t)

ThreadState AbortIpc_and_stop (ThreadId t, Word& sp, ip, flags)

[AbortIpc_and_stop_SpIpFlags]

As stop (), except any ongoing IPC send or receive operations are immediately aborted.

```

# **Support Functions:**

```

#include <|4/thread.h>

struct ThreadState { Word raw }

Bool ThreadWasHalted (ThreadState s)

Bool ThreadWasSending (ThreadState s)

Bool ThreadWasReceiving (ThreadState s)

Bool ThreadWasIpcing (ThreadState s)

Query the thread state returned from one of the stop () functions.

Word ErrorCode ()

Word ErrInvalidThread

```

22 THREADCONTROL

# 2.4 THREADCONTROL [Privileged Systemcall]

ThreadId dest → Word result

ThreadId SpaceSpecifier

ThreadId scheduler

ThreadId pager

void\* UtcbLocation

A privileged thread, e.g., the root server, can delete and create threads through this function. It can also modify the global thread ID (version field only) of an existing thread.

Threads can be created as *active* or *inactive* threads. Inactive threads do not execute but can be activated by active threads that execute in the same address space.

An actively created thread starts immediately by executing a short receive operation from its pager. (An active thread must have a pager.) The activeted thread expects a start message (MsgTag and two untyped words) from its pager. Once it receives the start message, it takes the value of MR  $_1$  as its new IP, the value of MR  $_2$  as its new SP, and then starts execution at user level with the received IP and SP. The new thread will execute on the same processor where the activating ThreadControl was invoked

Interrupt threads are treated as normal threads. They are active at system startup and can *not* be deleted or migrated into a different address space (i.e., SpaceSpecifier must be equal to the interrupt thread ID). When an interrupt occurs the interrupt thread sends an IPC to its pager and waits for an empty end-of-interrupt acknowledgment message (MR  $_0$ =0). Interrupt threads never raise pagefaults. To deactivate interrupt message delivery the pager is set to the interrupt thread's own ID.

# **Input Parameters**

# dest

Addressed thread. *Must be a global thread ID*. Only the thread number is effectively used to address the thread. If a thread with the specified thread number exists, its version bits are overwritten by the version bits of *dest id* and any ongoing IPC operations are aborted. Otherwise, the specified version bits are used for thread creations, i.e., a thread creation generates a thread with ID *dest*.

# **SpaceSpecifier** ≠ nilthread, dest not existing

*Creation.* The space specifier specifies in which address space the thread will reside. Since address space do not have own IDs, a thread ID is used as *SpaceSpecifier*. Its meaning is: the new thread should execute in the same address space as the thread *SpaceSpecifier*.

The first thread in a new address space is created with *SpaceSpecifier = dest*. This operation implicitly creates a new empty address space. Note that the new address space is created with an empty UTCB and KIP area. The space creation *must* therefore be completed by a SPACECONTROL operation before the thread(s) can execute.

# $SpaceSpecifier \neq nilthread, dest exists$

*Modification Only.* The addressed thread *dest* is neither deleted nor created. Modifications can change the version bits of the thread ID, the associated scheduler, the pager, or the associated address space, i.e., migrate the thread to a new address space.

# **SpaceSpecifier** = nilthread, dest exists

Deletion. The addressed thread dest is deleted. Deleting the last thread of an address space implicitly also deletes the address space.

# scheduler ≠ nilthread

Defines the scheduler thread that is permitted to schedule the addressed thread. Note that the scheduler thread must exist when the addressed thread starts executing.

THREADCONTROL 23

#### **scheduler** = nilthread

The current scheduler association is not modified. This variant is illegal for a creating THREAD-CONTROL operation.

pager ≠ nilthread

The pager of *dest* is set to the specified thread. If *dest* was inactive before, it is *activated*.

pager = nilthread

The current pager association is not modified.

If used with a creating THREADCONTROL operation, *dest* is created as an *inactive* thread.

$UtcbLocation \neq -1$

The start address of the UTCB of the thread is set to UtcbLocation. Upon thread activation the UTCB must fit entirely into the UTCB area of the configured address space, and must be properly aligned according to the UtcbInfo field of the kernel interface page. It is the application's responsibility to ensure that UTCBs of multiple threads do not overlap. Changing the UtcbLocation of an already active thread is an illegal operation. Note that since a newly created space has an empty UTCB area, it is not possible to activate a thread in an address space which has not been properly configured with SPACECONTROL.

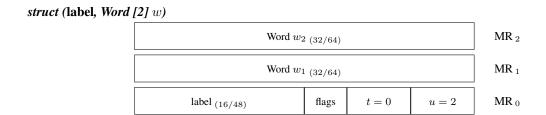

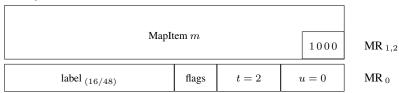

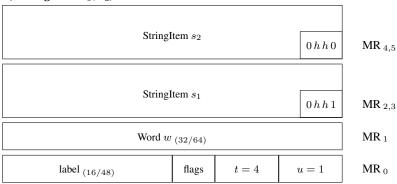

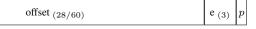

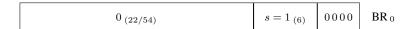

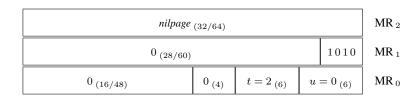

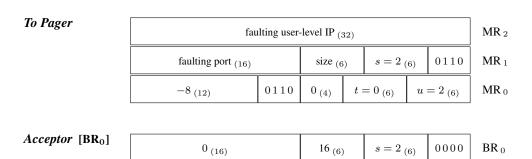

*UtcbLocation* = -1 The UTCB location is not modified.